[HotChips 2012 agenda exerpt, courtesy HotChips 24]

Vendors, Systems, and Processors Update

Normally, we don't release a consolidated update on the industry more than once a month, but there has been some significant updates.

IBM: POWER up?

By the time HotChips 24 arrives,

POWER 7+ should be about 1 year late, as Fujitsu SPARC remains #1 for over a year in the HPC charts.

Is IBM really going to talk-up POWER 7+, one year late, without releasing it? It is looking a lot like what happened to

Sun Microsystems with their ROCK processor, which was killed not long after there were multiple presentations on it, around the time of Oracle acquisition of Sun Microsystems.

IBM will also talk about their zNext processor, whatever that might be. Will POWER 7+ ever see the light of day?

Oracle: The SPARC is HotAround the time the industry was expecting IBM POWER 7+, Oracle release the SPARC T4 processor.

About 1 year later, during the same time that IBM will be talking about POWER 7+, Oracle is projected to release their SPARC T5 processor. The industry is hoping that Oracle will fulfull it's projection to release SPARC T5 in 2012, about 6 months ahead of time on their roadmap.

The SPARC T5 is supposed to be a glue-less 8 socket processor, adhering to SPARC V9 open standard, certified by

SPARC International. Different extensions are projected to be included, such as Oracle RDBMS number calculations in hardware and compression engines... both which will dramatically increase the performance of Oracle RDBMS's.

With the increase of Oracle RDBMS's also comes the dramatic increase in performance of software with embedded databases (which is basically everything enterprise grade.) Oracle has determined to sit on the top of the Enterprise Software performance stack and SPARC seems to be the delivery mechanism.

Why is Open Standards important in platforms? When a single vendor comes under pressure and can't deliver (i.e. IBM POWER 7+) - other vendors are free to "pick up the slack", earn a little money, and produce something of additional value for the consumer.

Fujitsu: SPARC On Top Today, Intending to Stay On Top

Fujitsu has a long history of producing SPARC CPU's, both for Sun Microsystems as well as for themselves. Fujitsu manufactured the first Sun SPARC processor, manufactured high-end systems for Sun and Oracle for the past half-decade, and has been holding the

#1 performance spot on the HPC 500 list.

Fujitsu released several iterations of their own SPARC CPU for massive super-computer (SPARC64 VIII fx, SPARC64 IX fx) Linux systems, as well as processors high-end (SPARC64 V, VI, and VII) Solaris systems. During HotChips 24 - they are projected to talk about their SPARC64 X processor!

The industry is hoping for a Solaris variant, based upon OpenSolaris fork like Illumos, to unify the Fujitsu and Oracle platforms, but there are no rumblings about that.

AMD: Embedding ARM in x64?

After reading about the Dell inclusion of ARM as an enterprise blade platform, the only thing more shocking would be the inclusion of ARM in a mainstream CPU vendor. Well, that day has come:

ARM is coming to AMD Opteron.

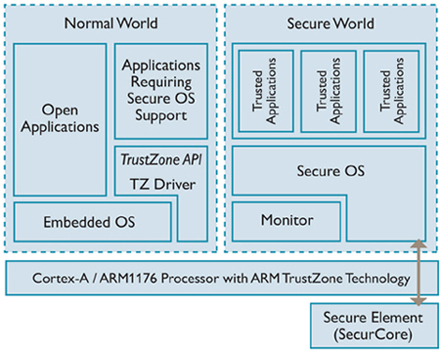

The use ARM in the AMD world seems to be targeting virtual computing. The

TrustZone feature of ARM may prove interesting for booting hypervisors or providing DRM (digital rights management).

HPC: Battle of the RISC's

Intel and AMD systems long ago took the top HPC spots. There was a general movement towards using graphics card co-processors to boost scores with specialized software. Some thought that the inclusion of ARM would help for future HPC systems, but with Fujitsu SPARC sitting on the top for a year, without any special co-processors, one may wonder whether graphics card vendors and special co-processor vendors have decided to sit out the super computer market, for awhile, since Fujitsu keeps upping the performance of their long-living SPARC open architecture.

Network Management Connection

With the rise of SPARC and ARM, one may wonder the impact for Network Management. ARM seemingly sits on most mobile devices, which all need to be managed. SPARC seemingly sits on the fastest Enterprise and HPC Systems. Network Management tool vendors will need to leverage these capabilities or at least manage them. Proprietary Intel is the volume proposition. AMD is the second-sourcing proposition for the proprietary Intel platform.

No network management vendor ignoring Intel, AMD, ARM, or SPARC are worth their weight in printed code.