|

| [SPARC International Inc. Member logo, courtesy Aurora VLSI] |

The SPARC architecture is perhaps the first and longest lasting open and mainstram computing architecture in human history. In Ocrober 2012, Network Management published a reminder for people to attend the "SPARC at 25" event at the Computer History Museum. In November of 2012, Network Management published an short article pointing to the replay of the historic events: SPARC at 25: Past, Present, and Future. Diana Reichardt published an article "SPARC at 25" in the bi-monthly printed Oracle Magazine, covering the event.

|

| [SPARC International, Inc. logo, courtesy sparc.org] |

Why SPARC?

Diana opens her article, regarding the event at the Computer History Museum, with the following question, "Why SPARC?" The article continues, with the following opening paragraph.

In 1987, a small startup called Sun Microsystems developed its own microprocessor, called SPARC, and introduced the Sun-4, the first computer based on the new chip. On November 1, 2012, many early SPARC team members, along with Oracle President Mark Hurd and Executive Vice President of Systems at Oracle John Fowler, convened at the Computer History Museum in Mountain View, California, for SPARC at 25: Past, Present, and Future. This event provided a look back at the history of SPARC and the early days of Sun. Stories from the participants, including all of the company’s founders, illustrated the complex nature of systems design and the challenges of launching a high-technology company in a fiercely competitive industry.The on-line reprint is no substitute for the written article, with it's high-resolution pictures of the event. This, of course, is no substitute for the video of the actual event, whose link was published in the former Network Management article.

|

| [Photos courtesy Oracle Magazine Jan/Feb 2013 Edition] |

If you do not have the time to watch the video of the creators of SPARC, on this 25th anniversary - Oracle published a highlights clip which is under 30 minutes. The highlights include current captains of industry, guiding SPARC today.

|

| [Start of the SPARC timeline, courtesy Oracle Corporation] |

Diana included a link at the end of her article titled "Explore the SPARC Time Line" which leads to an amazing timeline of events surrounding SPARC, that no person interested in systems should miss!

|

| [Oracle logo, courtesy Oracle Corporation] |

Who is Diana Reichardt?

Diana Reichardt is a senior writer at Oracle. Besides this Jan/Feb issue in Oracle Magazine, she had published a pair of articles "Conversations with Oracle Innovators" through Oracle Corporate Communications with Rick Hetherington.

Conversations with Oracle Innovators

Q&A with Rick Hetherington

By Diana Reichardt

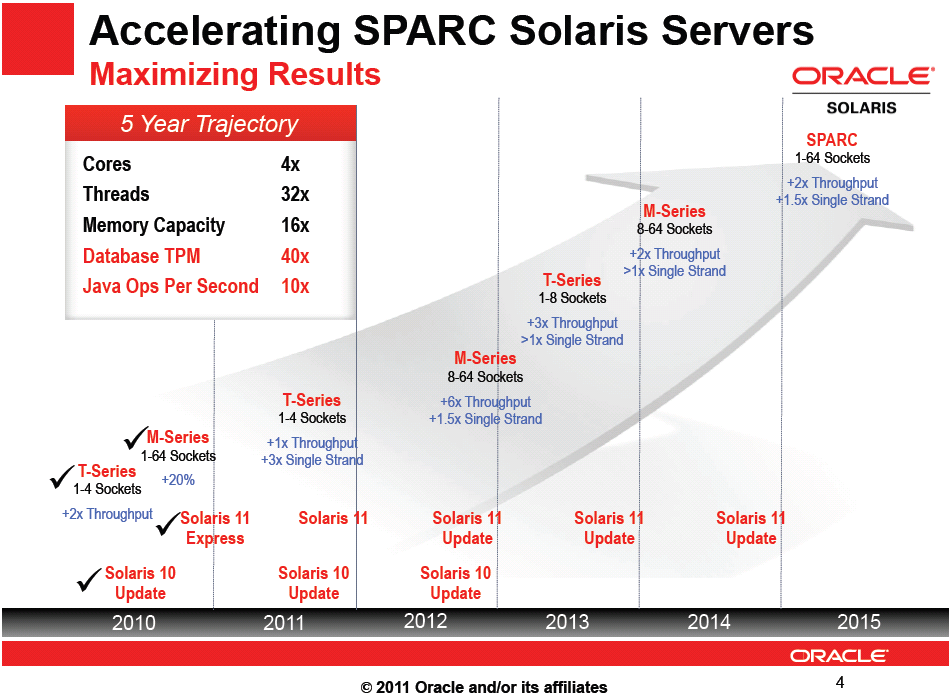

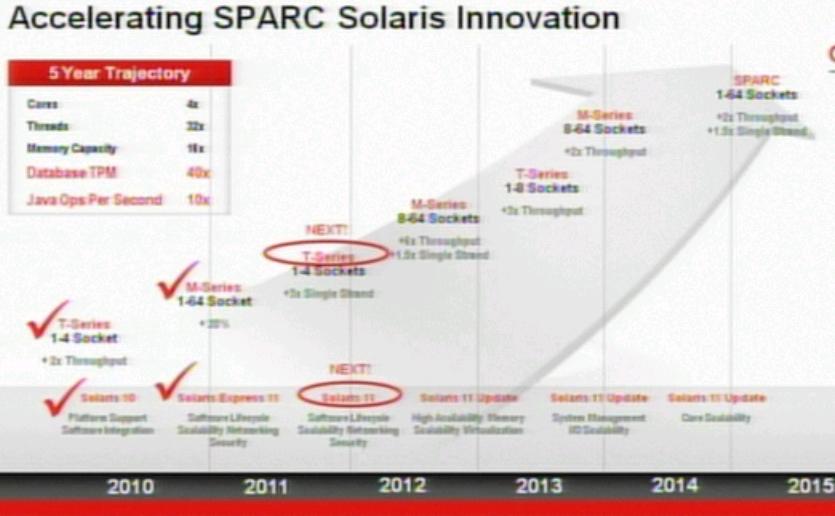

Rick Hetherington, Oracle’s vice president of hardware development, manages a team of architects and performance analysts who design Oracle’s M- and T-series processors. Hetherington’s team tracks the performance of these designs in great detail, from the moment they are conceived until they are released as products. In this interview, Hetherington explains the design process and how the team’s day-to-day work is focused on what SPARC customers will have in their data centers three to five years from now.

Conversations with Oracle Innovators

SPARC T4 Deep Dive With Rick Hetherington

By Diana Reichardt

Rick Hetherington, Oracle’s vice president of hardware development, manages a team of architects and performance analysts who design Oracle’s M- and T-series processors. In this interview, Hetherington describes the technical details of the new SPARC T4 processor and explains why he thinks it is going to be an eye-opener for the industry.Other fairly recent Oracle Magazine articles published by Diana include:

FEATUREDiana's writing is a pleasure to read.

Complete Power

By Diana Reichardt

Oracle Magazine: May/June 2011

SPARC hardware and the Oracle Solaris operating system: High-performance engine for mission-critical apps

COMMENT: Analyst’s Corner

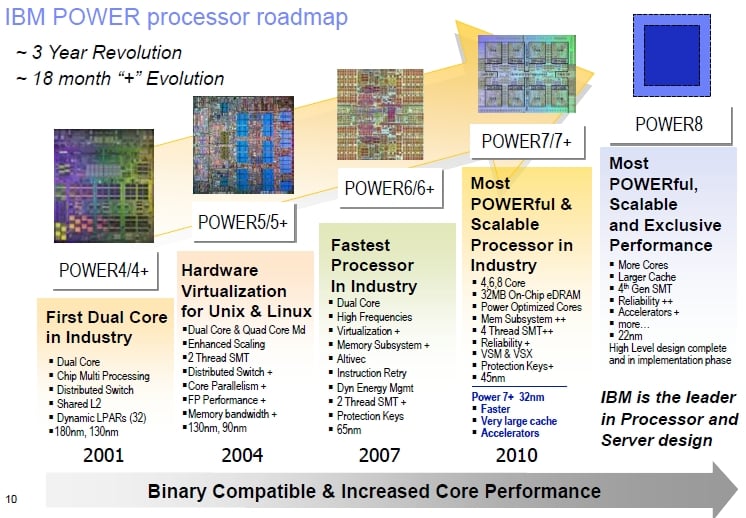

The SPARC/Oracle Solaris Platform Evolution

By Diana Reichardt

Oracle Magazine: May/June 2011

SPARC hardware and the Oracle Solaris operating system: High-performance engine for mission-critical apps

AT ORACLE: News

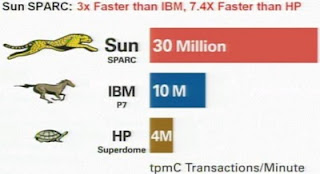

SPARC Torches Benchmark

By Diana Reichardt

Oracle Magazine: March/April 2011

Oracle’s new SPARC Supercluster, Oracle Exalogic Elastic Cloud T3-1B, and Oracle Solaris 11 break records and set new standards for performance and availability.

Concluding Thoughts:

No modern computing professional should be without the background and understanding of the history of computing from this period of time. The future always has elements of the past hinting forward. SPARC is no different, in this case - many of the ideas in modern computing history would not have ever existed, had it not been for SPARC innovators. More innovations are sure to come.