|

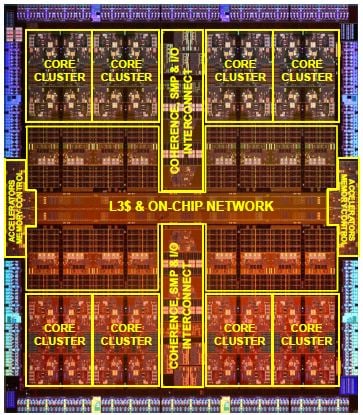

| [Oracle SPARC M7 Die, Courtesy The Register] |

Abstract:

The SPARC Processor family from Sun Microsystems had existed for nearly 30 years. SPARC was an early contender in the 64 bit processing market while most commodity processors were still 32 bits or fewer. With the purchase of Sun Microsystems by Oracle, SPARC development continued and produced the fastest processor on the planet. Oracle promised a day where Oracle would have one processor for both the T and M platforms. The latest generation of processor finally appears able to unify the T and M system lines. In December 2014, the Hot Chips 26 Symposium in 2014 conference material was released to the general public, illustrating what is coming in 2015. Happy New Year! |

| [M7 32x Socket Interconnect, courtesy Enterprise Tech] |

SPARC M7 at Hot Chips 26 in 2014:

Oracle announced during the Hot Chips conference that the new M7 processor and system would be released in 2015. Some notable reviews of the Oracle SPARC M7 included:- [2014-08-13] Timothy Pricket Morgan from Enterprise Tech Systems Edition

Oracle Cranks Up The Cores To 32 With Sparc M7 Chip

When asked about what the performance advantage would be comparing an InfiniBand or Ethernet cluster running Oracle RAC and the Sparc M7-Bixby setup using the non-coherent memory clusters, Fowler said that the difference “would not be subtle.” - [2014-08-18] Simon Sharwood from The Register

Oracle reveals 32-core, 10 BEEELLION-transistor SPARC M7

New chip scales to 1024 cores, 8192 threads 64 TB RAM, at speeds over 3.6GHz - [2014-08-12] James Niccolai from PC World

Oracle's Sparc M7 chip to supercharge in-memory computing

|

| [Oracle 2010 SPARC Road Map, courtesy Enterprise Tech] |

Hot Chips Oracle Presentation:

Stephen Phillips, the Senior Directory SPARC Architecture from Oracle, gave the presentation. He was involved in the architecture for T2+ (Victoria Falls) and later T-Series; M5, M6, M7 Processors, placing him in the cross-hairs of the delivery of the 2010 roadmap above. The Hot Chips 26 - August 12, 2014 (Big Iron Presentations) was included in Video (Video Start-End: 32:26-1:04:00) as well as High-Resolution PDF.It should be noted, that the clustering of the M7 produces a system capable of remote memory sharing with up to 64 sockets, make the formerly released 5 year road map (pictured above) astounding accurate, illustrating the intense fidelity that Oracle offered to the SPARC and UNIX communities.

|

| [M7 Decompression and Query Offload Engine, courtesy EnterpriseTech] |

SPARC M7 In-Silicon Enhancements:

As one watches the presentation and reviews the high resolution slides, the following is a short set of notes, highlighting what some would consider key aspects.Slide 3 - Recent history of SPARC

Slide 5 - M5 CPU - 20nm process; 32 Cores per Socket; 4 clustered cores; S4 enhanced core

Slide 6 - S4 Core - Dynamic Threading (1-8 threads) for speed & throughput; Faster Live migration

Slide 7 - Core Cluster - 1.5x Larger L2 Cache; 2x Greater Core Bandwidth

Slide 8 - Level 3 Cache & Network: 2.5x-5x Bandwidth; 25% Less Latency; HW Accelerator Access

Slide 9 - OVM "Aware" Solaris Process Groups by Core Cluster &, L3 Cache Partition

Slide 10 - Power aware in silicon; auto-adjusts voltage & frequency according to policy

Slide 11 - 2x-3x Memory Bandwidth; Live DIMM Retirement; Memory Lane Failover;

Greater than 2x PCIe performance

Slide 12 - Performance increase ~3x over M6

Slide 13 - Live Production Data Integrity Checking (for buffer overrun protection)

Slide 14 - Fine Grain Memory Migration for JAVA (for concurrent operations of middleware)

Slide 15 - Virtual Memory Masking for Java Runtime (embed object state into unused 64 bit)

Slide 16 - Decompression & Query accelerators for Oracle 12c (row & column for OLTP & OLAP)

Slide 17 - 8x Fused Decompression + Query Accelerators

Slide 18 - High performance for in-memory database without OS intervention

Slide 19 - 10-to-1 Decompression improvement of 1x query pipeline to 1x T5 (S3) Thread

Slide 20 - Third Party benefit through tool-chain

Slide 21 - Glue-less 1-8 socket support, like the T5

Slide 22 - SMP Scalability comprising 32 M7 SPARC Processors; 4 socket physical domains

Slide 23 - Reliable & Secure Shared Memory Clustering; 64 M7 sockets in a cluster; >1 failure tolerance

Slide 24 - Coherent Memory Cluster comprising 64 M7 SPARC Processors; secure foreign memory

The use of hardware application accelerators has proven to be a massive game changer in the industry for Oracle, as SPARC continues where others have failed.

No comments:

Post a Comment